概要

本頁では、Dフリップフロップ(DFF)について解説します。

DFFは、Dラッチの入力が出力に筒抜けになっている特性を改善し、クロック信号の立上りの瞬間しか出力が変化しないようにしたものです。

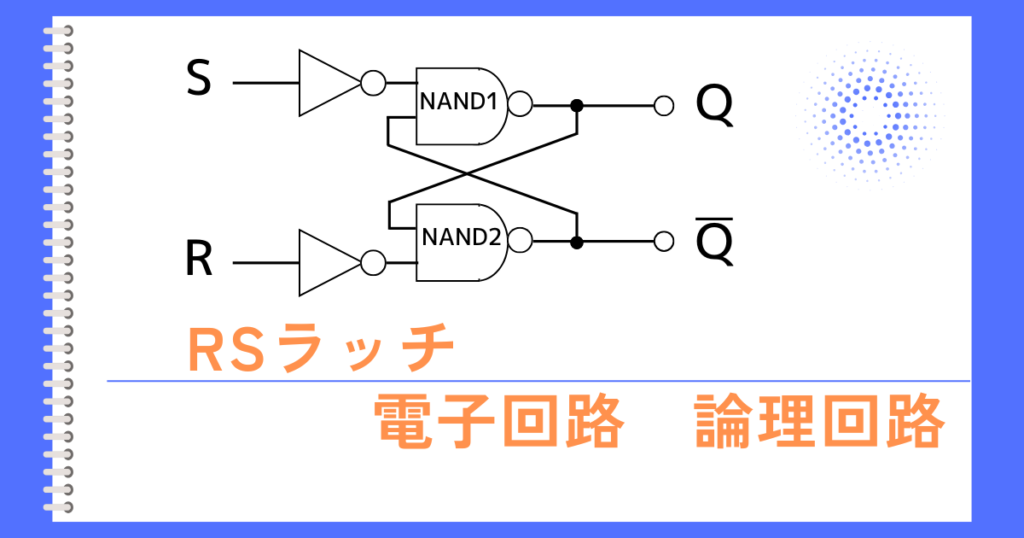

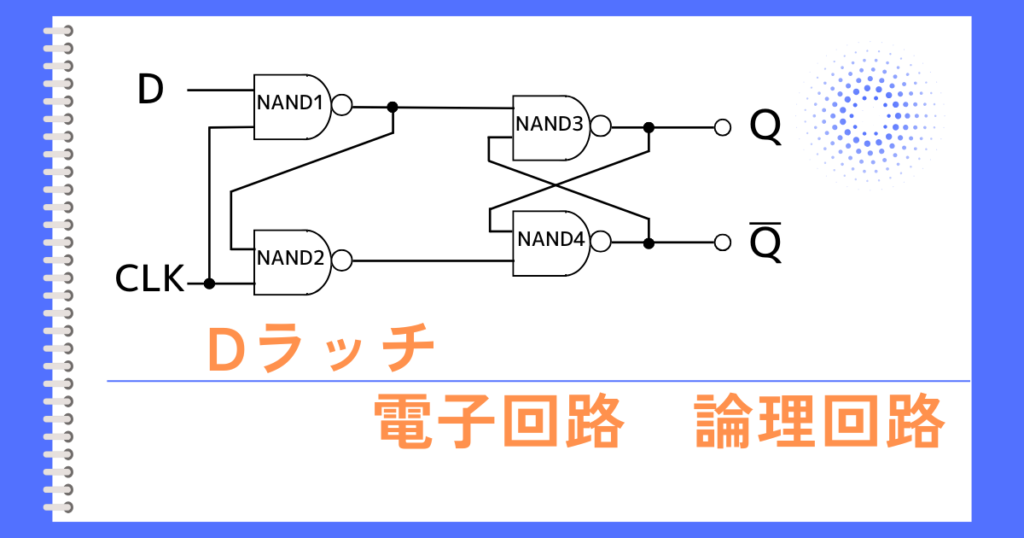

Dラッチ回路は、クロック信号が1(Hiレベル)の時、入力信号の0・1が変化すると、その出力も変化します。そのため、予期せぬタイミングで入力が変化すると、出力も一緒に変わってしまうので制御を難しくさせる原因となります。

そのため、クロック信号の立上り・立下りの瞬間しか出力が変化しないようにすることで、入力の予期せぬ変動の影響を受けずに、出力を確実なタイミングで変化させることができるようになります。

DFFは、シフトレジスタや、シリアル-パラレル変換、カウンター回路等、様々な所で応用されます。

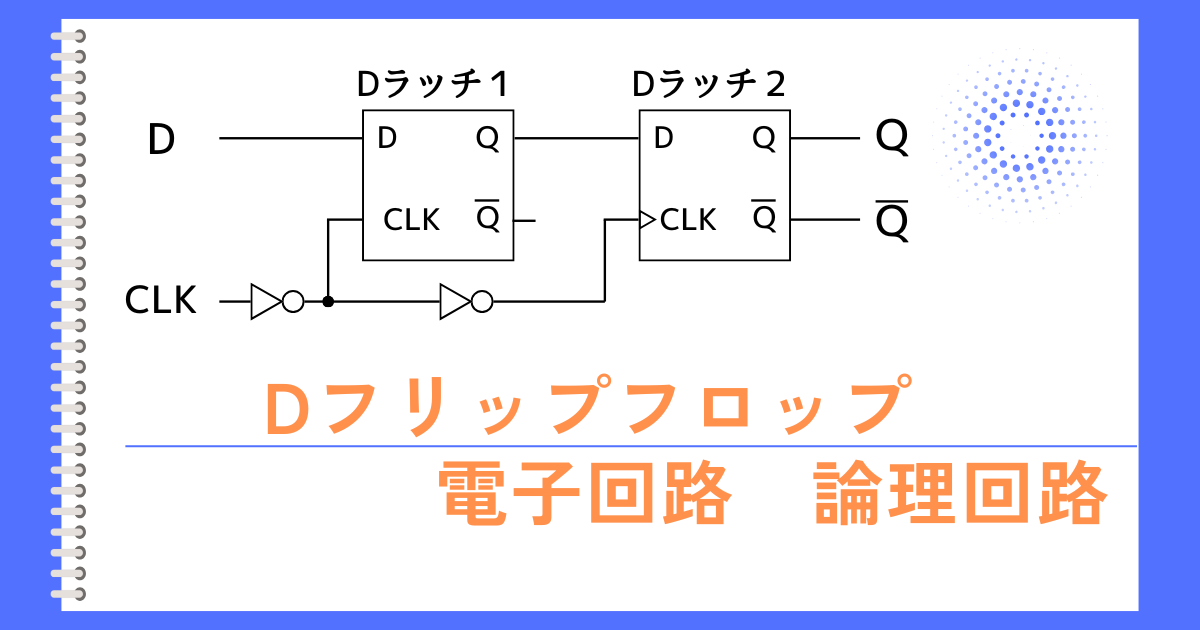

回路構造

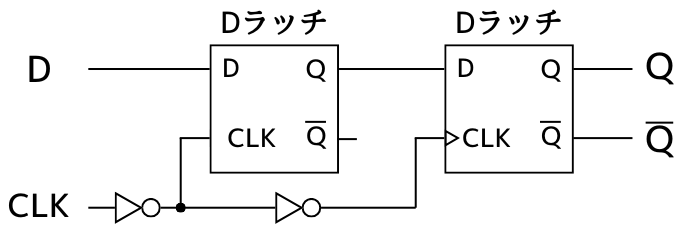

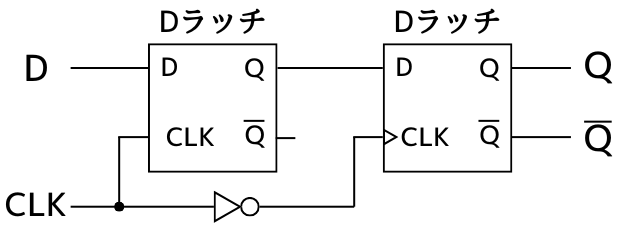

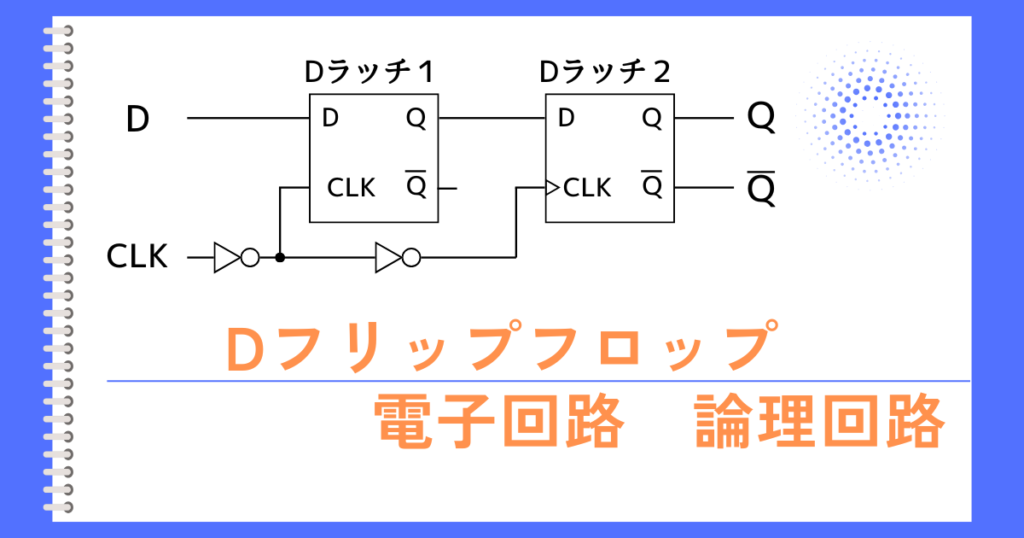

DFFは、2つのDラッチから作られます。

クロック信号(CLK)を1つはそのまま入力し、もう1つには反転入力します。

1つ目のDラッチの出力を、2つ目のDラッチに入力することで、DFFが完成します。

DFFの出力変化のタイミングは、クロックの入力の仕方によって、次の2つの型に分かれます。

・ポジティブエッジトリガ型:CLKが立上る瞬間に出力Qが変化する

・ネガティブエッジトリガ型:CLKが立下る瞬間に出力Qが変化する

ポジティブエッジトリガ型

回路図

真理値表

| \(D\) | \(CLK\) | \(Q\) | \(\overline{Q}\) |

| 0 | ⇧ | 0 | 1 |

| 1 | ⇧ | 1 | 0 |

ネガティブエッジトリガ型

回路図

真理値表

| \(D\) | \(CLK\) | \(Q\) | \(\overline{Q}\) |

| 0 | ⇩ | 0 | 1 |

| 1 | ⇩ | 1 | 0 |

動作解析(ネガティブエッジトリガ)

ネガティブエッジトリガ型のDFFの動作について解析します。

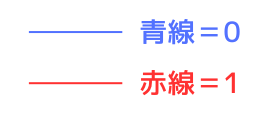

凡例

解析用の回路図は、青線を0、赤線を1とします。

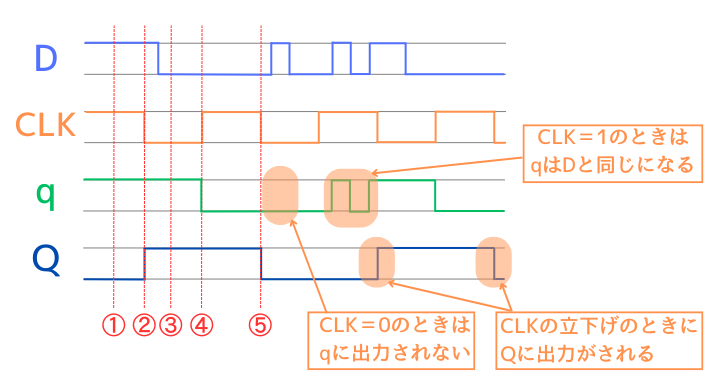

タイミングチャート

動作解析のためのサンプルのタイミングチャートを次の通りとします。

①~⑤のタイミングにおいて、回路の各部の状態を動作解析していきます。

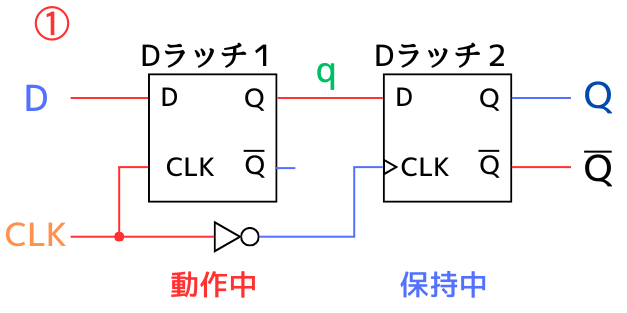

①入力(\(D=1\))、クロック(\(CLK=1\))の時

CLK=1であることから、

・Dラッチ1は、入力\(D=1\)が出力qに出力されます。

・Dラッチ2は保持中のため、出力は変化しません。

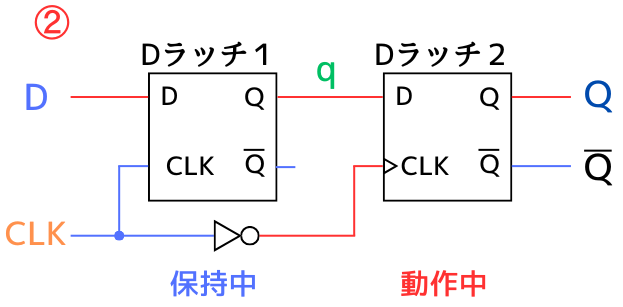

②入力(\(D=1\))、クロック(\(CLK=⇩\))の時

CLKが立下がり、CLK=0になるので、

・Dラッチ1は保持中のため、出力は変化しません。

・Dラッチ2は入力\(q=1\)が出力Qに出力されます。

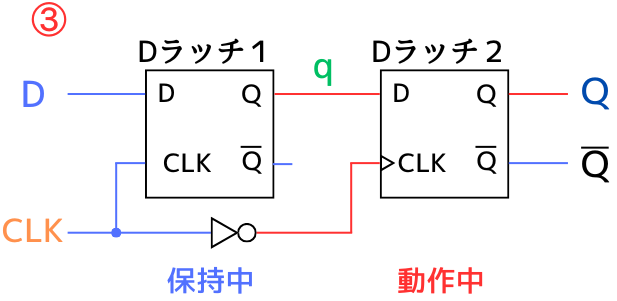

③クロック(\(CLK=0\))中に、入力(\(D=⇩\))となった時

CLK=0なので、

・Dラッチ1は保持中のため、入力\(D\)が変化しても、出力は変化しません。

・Dラッチ2は入力\(q=1\)が出力Qに出力され続けています。

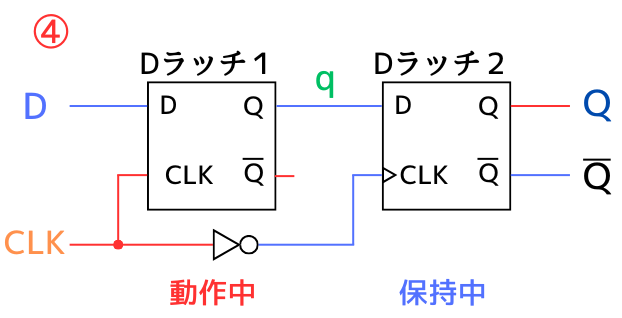

④ ③の状態から、クロック(\(CLK=⇧\))となった時

CLK=1になるので、

・Dラッチ1は動作中になるため、\(D=0\)が出力\(q\)に出力されます。

・Dラッチ2は保持中のため、出力は変化しません。

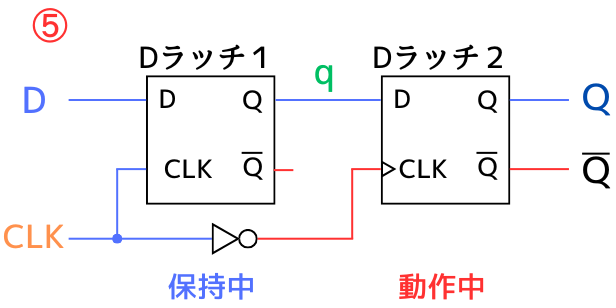

⑤ ④の状態から、クロック(\(CLK=⇩\))となった時

CLKが立下がり、CLK=0になるので、

・Dラッチ1は保持中のため、出力は変化しません。

・Dラッチ2は入力\(q=0\)が出力Qに出力されます。

関連記事

参考書

イラストがとても多く、視覚的に理解しやすいので、初学者に、お勧めなテキストです。

問題のページよりも、解説のページ数が圧倒的に多い、初学者に向けの問題集です。

問題集は、解説の質がその価値を決めます。解説には分かりやすいイラストが多く、始めて電気に触れる人でも取り組みやすいことでしょう。

本ブログの管理人は、電験3種過去問マスタを使って電験3種を取りました。

この問題集の解説は、要点が端的にまとまっていて分かりやすいのでお勧めです。

ある程度学んで基礎がある人に向いています。

コメント